CCN / Departamento de Física

Disciplina Eletrônica básica

Técnicas digitais

#### Experimento 1

#### **Objetivo:**

Estabelecer a tabela verdade para o gate básico AND.

Todo circuito lógico executa uma expressão Booleana e, por mais complexo que seja, é formado pela interligação de portas lógicas básicas. Podemos obter a expressão Booleana que é executada por um circuito lógico qualquer.

Nesta experiência será examinado o bloco (ou Gate ) básico E.

Expressão Lógica

S = A.B = AB onde o ponto significa AND. Pode-se omitir o ponto como na expressão AB que significa A e B.

A função AND pode ser definida como "saída  $\mathbf{1}$  só se todas as entradas forem  $\mathbf{1}$ " e o bloco **AND** funciona deste modo, isto é, a saída será + ( nível alto ) somente quando todas as entradas estiverem no nível + ( alto ).

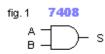

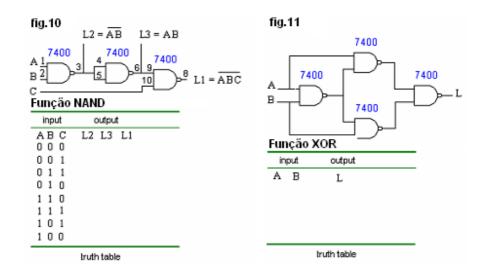

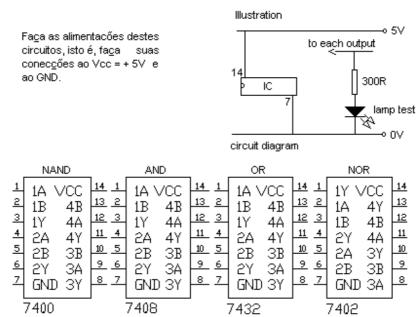

A fig.1 mostra o símbolo e a tabela verdadeira para o bloco AND.

#### Material e Componentes

Fonte de alimentação – 5V d.c.

Resistor – 270R / 1/8W Circuito – CI 7408

LED

Conectores

Protoboard

#### **Procedimento:**

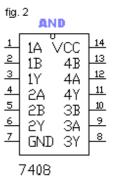

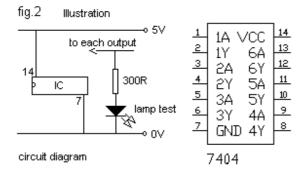

1.Conecte no board, o CI 7408, fig.2, que consta de quatro blocos **AND**, cada um com duas entradas.

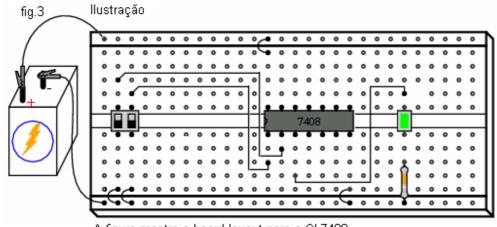

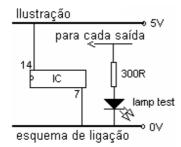

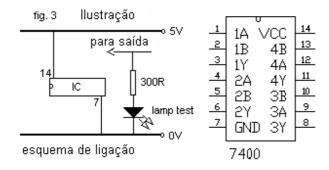

2.Ligue o pino 14 a +5V e o pino 7 ao "COMUM", fig.3.

#### Nota:

Na série 74, todos os pinos de entrada sem conexão funcionam com nível 1.

No caso da montagem prática as lâmpadas deverão ser conectadas ao circuito mediante resistores calculados conforme o Vcc. Lâmpada acesa vale 1.

A fig.3 mostra como conectar no "board" um simples circuito para teste.

Prática 11

| Bloco AND   |   |        |  |

|-------------|---|--------|--|

| inputs o    |   | output |  |

| Α           | В | ន      |  |

| 0           | 0 | 0      |  |

| 0           | 1 | 0      |  |

| 1           | 1 | 1      |  |

| 1           | 0 | 0      |  |

| truth table |   |        |  |

A figura mostra o board layout para o CI 7408

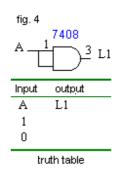

- 3. Monte o circuito da fig.4 e complete a tabela verdade.

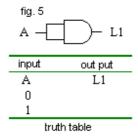

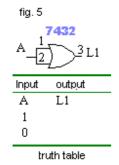

- **4**.Monte o circuito da fig.5 e complete a tabela verdade.

| inp | uts | output   |

|-----|-----|----------|

| Α   | В   | L (lamp) |

| 0   | 0   |          |

| 0   | 1   |          |

| 1   | 1   |          |

| 1   | 0   |          |

truth table

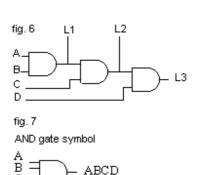

5. Monte o circuito da fig. 6 e complete a tabela verdade.

fig. 8

| _ | _           | _   |   |         |          |           |

|---|-------------|-----|---|---------|----------|-----------|

|   | inpu        | uts |   |         | output   |           |

| Α | В           | С   | D | L1 = AB | L2 = ABC | L3 = ABCD |

| 0 | 0           | 0   | 0 |         |          |           |

| 0 | 0           | 0   | 1 |         |          |           |

| 0 | 0           | 1   | 1 |         |          |           |

| 0 | 0           | 1   | 0 |         |          |           |

| 0 | 1           | 1   | 0 |         |          |           |

| 0 | 1           | 1   | 1 |         |          |           |

| 0 | 1           | 0   | 1 |         |          |           |

| 0 | 1           | 0   | 0 |         |          |           |

| 1 | 1           | 0   | 0 |         |          |           |

| 1 | 1           | 0   | 1 |         |          |           |

| 1 | 1           | 1   | 1 |         |          |           |

| 1 | 1           | 1   | 0 |         |          |           |

| 1 | 0           | 1   | 0 |         |          |           |

| 1 | 0           | 1   | 1 |         |          |           |

| 1 | 0           | 0   | 1 |         |          |           |

| 1 | 0           | 0   | 0 |         |          |           |

|   | truth table |     |   |         |          |           |

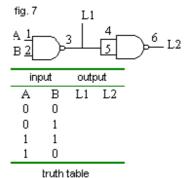

Usando o CI 7408 pode-se fazer circuitos **AND** com mais de três entradas, fig. 6 - 7. Por exemplo: para executar a função lógica **L3** = ABCD fazemos **L3** = (AB) C D.

No caso do circuito **AND** de quatro entradas, fig.6, com três blocos **E** de duas entradas, entre as entradas e a saída **L3** existe a demora de três blocos **AND**. Isto algumas vezes pode ser inconveniente; um método usado para reduzir esta demora é o indicado no circuito da fig.8.

Note que a função lógica AND é definida por: "Saída 1 se todas as entradas forem 1"

ABCD

#### Responda:

Como obter "3-input **AND** gate" usando dois "2-input **AND** gates" ? Referências:

AntónioJ.; Padilla G. Sistemas digitais. Portugal, Mc Graw-Hill, 1993

Palmer J.; Perlman D.Introduction to Digital Systems. USA,Mc Graw-Hill,1993

Plant, Macolm. Basic Eletronics, London, SCDC Publications.

Prof. Franklin

CCN / Departamento de Física

Disciplina Eletrônica Básica

Técnicas Digitais

#### Experimento 2.

#### **Objetivo:**

Estabelecer a tabela verdade para o gate  $\mathbf{OR}$

Introdução:

A função  $\mathbf{OR}$  é definida como aquela que tem saída 1 quando houver uma ou mais entradas 1. Na fig.1 tem-se o símbolo  $\mathbf{OR}$  e a tabela verdade.

Para um "multiple input **OR** gate", um alto em qualquer das entradas dá um alto na saída.

#### **Material e Componentes**

Fonte de alimentação – 5V d.c. Resistor – 270R / 1/8W Circuito – CI 7432

LED

Conectores Protoboard

# OR 1A VCC 14 1B 4B 13 1Y 4A 12 2A 4Y 11

Prática 11

5 2B 3B 10 6 2Y 3A 9 7 GND 3Y 8

7432

| inp | uts |   | outp | jut |

|-----|-----|---|------|-----|

| Α   | В   | С | L1   | L2  |

| 0   | 0   | 0 |      |     |

| 0   | 0   | 1 |      |     |

| 0   | 1   | 1 |      |     |

| 0   | 1   | 0 |      |     |

| 1   | 1   | 0 |      |     |

| 1   | 1   | 1 |      |     |

| 1   | 0   | 1 |      |     |

| 1   | 0   | 0 |      |     |

|     |     |   |      |     |

truth table

#### Experiência:

1. Conecte o CI 7432 no board.

truth table

- 2.Ligue o pino 14 a + 5V e o pino 7 ao comum.

- 3.Execute o circuito da fig.2a e "check" a tabela verdade.

- **4.**Usando o circuito anterior, desconecte o pino 2 da chave B, fig.2b e complete a tabela.

Após completar a tabela observe que a saída L independe de A, o pino 2 que está desconectado (flutuando) está funcionando na entrada do bloco como se tivesse o nível lógico 1. E isto pode ser considerado uma regra para os CIs da série 74XX. Vemos que neste caso o circuito não executa função nenhuma (saída sempre 1).

Na **série 74**, todos os pinos de entrada sem conexão funcionam como 1.

Blocos OR de várias entradas.

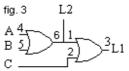

5.Monte no board o circuito da fig.3. Este circuito executa  $\ a$  função  $\ L1=A+B+C$  .

Este circuito é também chamado de **OR** de dois níveis.

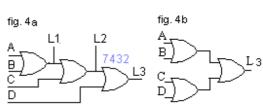

6.O circuito da fig. 4a executa a função

L3 = A + B + C + D. "Check" o funcionamento.

Note que podemos construir o circuito de acordo com a equação equivalente L3 = (A+B) + (C+D), fig.4b.

| inputs  |        | output              |

|---------|--------|---------------------|

| ABCD    | L1=A+B | L2=A+B+C L3=A+B+C+D |

| 0000    |        |                     |

| 0001    |        |                     |

| 0 0 1 1 |        |                     |

| 0 0 1 0 |        |                     |

| 0 1 1 0 |        |                     |

| 0 1 1 1 |        |                     |

| 0 1 0 1 |        |                     |

| 0100    |        |                     |

truth table

Prof. Franklin Cruzio

CCN / Departamento de Física

Disciplina Eletrônica Básica

Técnicas Digitais

#### Experimento 3.

#### **Objetivo:**

Estabelecer a tabela verdade para o gate Not (inversor)

#### Introdução:

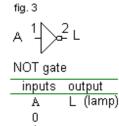

A implementação de circuitos lógicos, eventualmente requer a inversão de um sinal ou função, isto é, um "input of logic 1 gives an output of logic 0". Para este fim usa-se o Gate **Not** (Não). Também conhecido como inversor este bloco lógico é o mais simples de todos os gates, tendo somente uma entrada e uma saída. O símbolo e a tabela de funcionamento (função executada do circuito **Not**) estão mostrados na fig.1.

#### Material

$\begin{array}{lll} Fonte \ de \ alimenta \\ \hline \text{Resistor} & -5 \text{V d.c.} \\ \hline \text{Circuito} & -270 \text{R} \ / \ 1/8 \text{W} \\ \hline \text{CIRCUITO} & -\text{CI} \ 7404 \end{array}$

LED Conectores

Protoboard

#### **Procedimento:**

- 1. Conecte um CI 7404 que consta de seis inversores, no "board".

- 2.Ligue o pino 14 do CI a + 5V e o pino 7 ao comum, fig.2.

- 3.Usando os terminais 1 e 2, faça as ligações indicadas no circuito da fig.3.

- **4.**Ligue a chave A para 0, anote o resultado de L na tabela . A seguir ligue A para 1 e anote o resultado de L na tabela verdade.

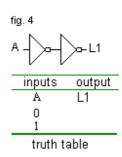

- **5**. Faça a montagem do circuito fig. 4 e anote o resultado na tabela verdade.

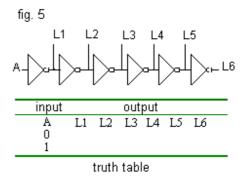

- **6**. Faça a montagem do circuito fig. 5 e anote o resultado na tabela verdade.

Prática 11

NOT gate symbol

| $= \overline{A}$ |

|------------------|

| 1                |

| 0                |

|                  |

truth table

truth table

7. Verifique na tabela do circuito da fig.5  $\,$  que a saída de cada bloco  $N\tilde{A}O$  é o inverso da entrada.

NOTA: Uma série de blocos NÃO tem várias aplicações práticas, por exemplo, como circuito de demora, outra aplicação é o buffer; a cada especificação de saída, de um dado bloco lógico indica quantas entradas de blocos lógicos de mesma família podem ser conectados à sua saída, isto é denominado de FANOUT, por exemplo, para Cis do tipo TTL o FANOUT típico é 10. Se a configuração do circuito exigir mais de 10 blocos, podem-se usar inversores como **buffer** para aumentar o FANOUT, conforme mostra a fig.6.

#### Resumo:

O bloco NÃO (inversor) é usado para inverter o sinal de entrada. Demoras (delays) com inversão de sinal podem ser obtidas usando-se um número ímpar de inversores em série. A demora total será a soma das demoras dos blocos. Os inversores podem ser usados também como buffers.

fig. 6

saída

de um circuito

#### Referências:

AntónioJ.;Padilla G. Sistemas digitais. Portugal, Mc Graw-Hill, 1993 Palmer J.;Perlman D.Introduction to Digital Systems. USA,Mc Graw-Hill,1993 Plant, Macolm. Basic Eletronics, London, SCDC Publications.

Prof. Franklin

CCN / Departamento de Física Disciplina Eletrônica Básica Técnicas digitais

Experimento 4.

Gate **NAND** (NÃO-E)

#### **Objetivo:**

Estabelecer a tabela verdade para o gate **NAND**. Estabelecer a tabela verdade para o gate **XOR**.

#### Introdução

A função NÃO-E pode ser definida como saída **0** somente se ambas entradas são **1**. Simbolicamente o bloco NÃO-E pode ser representado pelo símbolo de um bloco **E** seguido de um pequeno círculo que indica uma inversão. A função NÃO-E também pode ser formada por um bloco **E** seguido de um NÃO, fig.2.

O Bloco NÃO-E é um circuito universal. Com o bloco NÃO-E, pode-se executar qualquer circuito. Mostraremos a execução das funções básicas usando este bloco.

A fig.1 mostra o símbolo e a tabela verdade do bloco **NAND**. A expressão Booleana é:  $S = \overline{AB}$

fig. 2

$$A \longrightarrow S \equiv A \longrightarrow S$$

#### Material

Fonte de alimentação – 5V d.c. Resistor – 270R / 1/8W

Circuito – CI 7400

LED Conectores Protoboard

#### **Procedimento:**

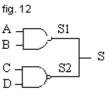

- 1. Conecte o CI7400 ao "board", como ilustra a fig. 3.

- 2. Monte no "board" o circuito da fig.4 e complete a tabela verdade.

- 3. Execute o circuito da fig.5 e preencha a tabela de funcionamento.

**Nota**: - Observe que a função executada, circuito da fig.5, é a função NOT (um dos pinos flutuando funciona com nível  $\bf 1$ )

Prática 11

| in          | out | output               |  |

|-------------|-----|----------------------|--|

| Α           | В   | $S = \overline{A.B}$ |  |

| 0           | 0   | 1                    |  |

| 0           | 1   | 1                    |  |

| 1           | 1   | 0                    |  |

| 1           | 0   | 1                    |  |

| truth table |     |                      |  |

| input       |   | output   |  |  |

|-------------|---|----------|--|--|

| Α           | В | L (lamp) |  |  |

| 0           | 0 |          |  |  |

| 0           | 1 |          |  |  |

| 1           | 1 |          |  |  |

| _1_         | 0 |          |  |  |

| truth table |   |          |  |  |

1

Então na equação com o pino  $11=\overline{12.13}$  que corresponde no circuito anterior a  $L=\overline{A.1}=\overline{A}$ . O mesmo resultado poderia ser obtido se conectássemos o pino 13 a um ponto de nível 1, ou pino 13 a entrada A, fig.6.

Na Álgebra de Boole consta o teorema A.A=A. Com este teorema observamos que a função executada pelo circuito anterior é a função NÃO, isto é:

o pino

$$11 = 12.13$$

;  $L = A.A = A$

4. Monte o circuito da fig.7 e preencha a tabela.

Observe que L1 = AB e que L2 é o sinal de L1 invertido, isto é, L2

executa a função NÃO com L1, ou seja, L2 = L1 = AB. A Álgebra de Boole mostra que uma expressão submetida a duas negações resulta na expressão original (isto é, duas barras sobre a expressão não alteram a

expressão), assim sendo  $L2 = \overline{AB} = AB$ . Vemos então que L2 é saída de um circuito E, portanto o circuito da fig.7 executa a função E.

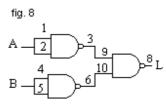

5. Monte o circuito da fig.8 e complete a tabela.

Note que a função executada é a função OU, isto é, L=A+B. Pode-se explicar isto mediante o Teorema de DE MORGAN:

a)

$$\overline{X+Y} = \overline{X} \cdot \overline{Y}$$

b)

$$\overline{X.Y} = \overline{X} + \overline{Y}$$

Note que no circuito anterior o pino  $3 = \overline{A}$  e o pino  $6 = \overline{B}$

$$L = \overline{3.6} = \overline{\overline{A}\overline{B}}$$

pelo teorema de De Morgan,

$\equiv = L = A + B = A + B$  mostrando que o circuito anterior executa a função OU.

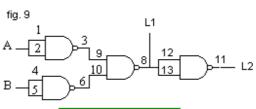

**6**. Monte o circuito da fig. 9 e preencha a tabela.

Observe que L1 corresponde à saída de um circuito OU, isto é, L1 = A + B e L2 é a negação de L1, isto é L2 =  $\overline{L1}$  =  $\overline{A+B}$ , então L2 é a saída de um circuito NÃO-OU. O circuito da fig.9 executa a função NÃO-OU.

- 7. Com o CI 7400 execute o circuito da fig.10, L1 = A.BC e complete a tabela.

- **8**. Conecte o **CI 7400** ao board. Monte o circuito da fig.11. Verifique que a função executada é a função **XOR**. Escreva a expressão simplificada do circuito.

| input       |   | output |  |  |

|-------------|---|--------|--|--|

| Α           | В | L      |  |  |

| 0           | 0 |        |  |  |

| 0           | 1 |        |  |  |

| 1           | 1 |        |  |  |

| 1           | 0 |        |  |  |

| truth table |   |        |  |  |

| İГ          | input |    | out |  |  |

|-------------|-------|----|-----|--|--|

| Α           | В     | L1 | L2  |  |  |

| 0           | 0     |    |     |  |  |

| 0           | 1     |    |     |  |  |

| 1           | 1     |    |     |  |  |

| 1 0         |       |    |     |  |  |

| truth tabla |       |    |     |  |  |

Com circuitos NAND pode-se executar qualquer função lógica.

#### Nota:

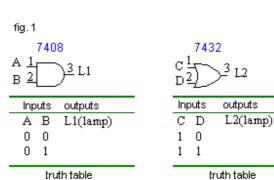

Lógica por Fios ou "Wired Logic":

O gate AND por fios pode ser formado ligando-se a saída de dois ou mais blocos TTL a um só ponto, conforme indica a fig.12 e a correspondente tabela. Para circuitos TTL não é uma boa prática, devendo ser evitada (exceto quando se usam blocos TTL especiais, chamados de coletor aberto), pois em geral provoca um consumo excessivo. A conexão das duas saídas a um só ponto funciona como um bloco E, isto é, se algumas das saídas S1 ou S2 estiver no nível (baixo), a saída S estará 0 (baixa). Em outras palavras, S só será  $\frac{1}{2}$  (alto) se S1 for  $\frac{1}{2}$  (alto), e S2 for 1 (alto), conforme mostra a tabela; então  $\frac{1}{2}$  S = S1.S2, mas  $\frac{1}{2}$  S1 =  $\frac{1}{2}$  E =  $\frac{1}{2}$  C =  $\frac{1$

#### Referências:

António J. Padilla G. Sistemas digitais. Portugal, Mc Graw-Hill, 1993 Palmer J.; Perlman D.Introduction to Digital Systems. USA, Mc Graw-Hill, 1993 Plant, Macolm. Basic Eletronics, London, SCDC Publications

Prof. Franklin

CCN / Departamento de Física Disciplina Eletrônica Básica

Tecnicas Digitais Prática 11

#### Experimento 5.

Objetivo: Verificar alguns teoremas da Álgebra de Boole.

#### Introdução:

Todos os circuitos digitais funcionam ao conectar nas suas entradas sinais digitais. As saídas são também sinais elétricos do mesmo tipo. Estes sinais são formados exclusivamente por dois níveis de tensão que correspondem aos dois estados estáveis ( corte e saturação ) dos elementos eletrônicos básicos que constituem as portas lógicas e outros blocos integrados.

Qualquer informação que se deseja tratar, processar ou armazenar usando sistemas digitais deverá ser codificado num tipo de linguagem adequada. Na pratica, qualquer numero, letra, símbolo, instrução ou operação é convertido num conjunto de sinais elétricos digitais.

A álgebra de Boole é fundamental para se trabalhar com circuitos lógicos. Os teoremas usuais da álgebra de Boole são:

Os circuitos seguintes examinam alguns teoremas da Álgebra de Boole.

#### Experimento

Procedimento: Conecte os circuitos integrados seguintes no board: 1x 7400 1x7402 1x 7408 1x7432.

1. Monte no board os circuitos da fig. 1.

Depois de completadas as tabelas, obtém-se no caso do gate AND, L1=0 (off). Verificando o teorema 0.X=0 no caso do circuito A=0 e B=X. Note que 0 vezes qualquer valor é 0. No caso do gate OR obtém-se L2=1 (on) verificando o teorema 1+X=1, isto é, "1 mais qualquer valor é 1", onde no circuito, C foi fixado em 1 e D é o X do Teorema .

#### 2. Monte no board o circuito da fig. 2

Neste caso o valor de L1 é igual a B como se pode verificar na tabela, o que confere o teorema: 1.X = X, visto que X = B e A = 1.

$$\begin{array}{lll} 1.B=B \\ 1.0=0 & B=0 & \text{Pelos postulados temos mostrado que a saída \'e} \\ 1.1=1 & B=1 & \text{igual a B}. \end{array}$$

truth table

### 3.Monte o circuito da fig. 3 e complete a tabela. Verifique o teorema 0 + X = X.

# 5. Monte o circuito da fig. 5 e complete a tabela. Verifique o teorema X + X = X.

## 4. Monte o circuito da fig. 4 e complete a tabela. Verifique o teorema XX = X.

# 6. Monte o circuito da fig. 6 e complete a tabela Verifique o teorema $X\overline{X} = 0$ .

7. Monte o circuito da fig.  $\frac{7}{X}$  e complete a tabela. Verifique o teorema  $X + \frac{7}{X} = 1$ .

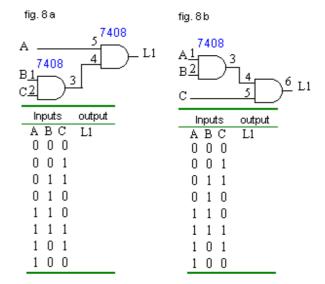

8. Monte os circuitos da fig. 8 e complete a tabela.

No primeiro caso, circuito da fig. 8 a, tem-se o circuito A(BC)., e no segundo caso, circuito da fig. 8 b, tem-se o circuito (AB)C Comparando-se as duas tabelas, observa-se que (AB)C = A(BC). De modo análogo, poderíamos mostrar, usando blocos OU, que (A+B)+C=A+(B+C).

- 9. Monte os circuitos da fig. 9 e complete as tabelas. Nos circuitos: L1 =  $\overline{AB}$  e L2 =  $\overline{A}$  +  $\overline{B}$  . Verifique o Teorema de De Morgan  $\overline{AB}$  =  $\overline{A}$  +  $\overline{B}$  .

- 10. Monte os circuitos da fig. 10 e complete a tabela. Verifique o Teorema de De Morgan  $\overline{A+B} = \overline{A}$ .

fig. 9

A

$$\frac{1}{B}$$

B  $\frac{7400}{B}$

B  $\frac{3}{2}$

L1 =  $\overline{AB}$

$\frac{\overline{A}}{B}$

$\frac{1}{2}$

$\frac{17432}{2}$

3 L2

Inputs outputs

A B L1 L2

0 0

0 1

1 1

1 0

truth table

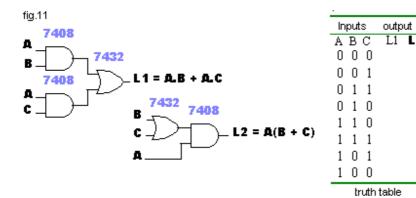

11. Monte os circuitos da fig. 11 e complete a tabela. Verifique o teorema AB + AC = A(B + C).

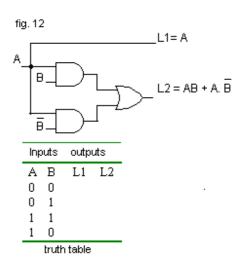

12.Monte o circuito da fig. 12 e complete a tabela. Verifique o teorema AB + A.  $\overline{B}$  = A

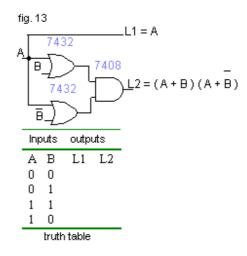

13.. Monte o circuito da fig. 13 e complete a tabela. Verifique o teorema  $(A + B) (A + \overline{B}) = A$ .

L1 L2

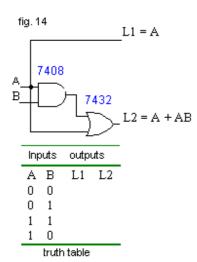

14. Monte o circuito da fig. 14 e complete a tabela. Verifique o Teorema A + AB = A.

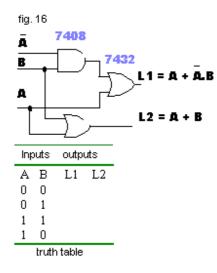

16. Monte o circuito da fig. 16 e complete a tabela. Verifique o teorema  $A + \overline{A}B = A + B$ .

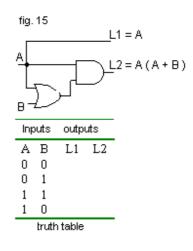

15. Monte o circuito da fig. 15 e complete a tabela. Verifique o Teorema A(A+B) = A.

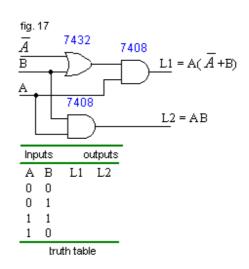

17. Monte o circuito da fig.  $\overline{17}$  e complete a tabela. Verifique o teorema A ( $\overline{A}$  + B) = AB.

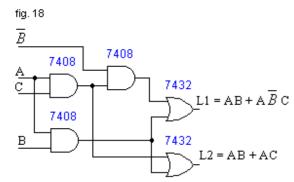

#### 18. Monte o circuito da fig. 18 . Verifique o teorema

$$AB + A\overline{B}C = AB + AC.$$

| Inp | uts | outputs |

|-----|-----|---------|

| ΑI  | 3 C | L1 L2   |

| 0 1 | 0 0 | 1       |

| 0   | 0 1 |         |

| 0   | 1 1 |         |

| 0   | 1 0 | 1       |

| 1   | 1 0 | l       |

| 1   | 1 1 |         |

| 1   | 0 1 |         |

| 1   | 0 0 | l       |

truth table

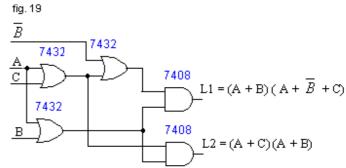

19.Monte o circuito da fig. 19. Verifique o teorema

$$(A + B) (A + \overline{B} + C) = (A+B) (A + C).$$

| Inputs |   | outpo | uts |  |

|--------|---|-------|-----|--|

| AB     | C | L1    | L2  |  |

| 0 0    | 0 |       |     |  |

| 0 0    | 1 |       |     |  |

| 0 1    | 1 |       |     |  |

| 0 1    | 0 |       |     |  |

| 1 1    | 0 |       |     |  |

| 1 1    | 1 |       |     |  |

| 1 0    | 1 |       |     |  |

| 1 0    | 0 |       |     |  |

|        |   |       |     |  |

truth table

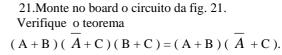

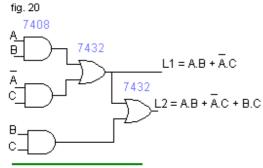

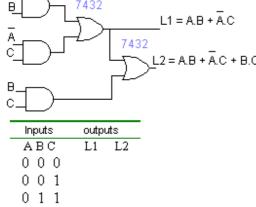

20. Monte no board o circuito da fig. 20 Verifique o teorema

$$A.B + \overline{A}.C + B.C = \overline{A}.C + A.B$$

| A 7432<br>B C C C C C C C C C C C C C C C C C C C | 7408    | L1 = (A + B) (Ā + C)  7408  L2 = (A + B) (Ā + C) (B + C) |

|---------------------------------------------------|---------|----------------------------------------------------------|

| Inputs                                            | outputs |                                                          |

| ABC                                               | L1 L    | 2                                                        |

| 0 0 0                                             |         |                                                          |

| 0.0.1                                             |         |                                                          |

| Input       | 8 | outputs |    |  |  |

|-------------|---|---------|----|--|--|

| AB          | C | L1      | L2 |  |  |

| 0 0         | 0 |         |    |  |  |

| 0 0         | 1 |         |    |  |  |

| 0 1         | 1 |         |    |  |  |

| 0 1         | 0 |         |    |  |  |

| 1 1         | 0 |         |    |  |  |

| 1 1         | 1 |         |    |  |  |

| 1 0         | 1 |         |    |  |  |

| 1 0         | 0 |         |    |  |  |

| truth table |   |         |    |  |  |

fig. 21

#### Referências:

truth table

AntónioJ.;Padilla G.Sistemas digitais. Portugal, Mc Graw-Hill, 1993 Palmer J.; Perlman D.Introduction to Digital Systems. USA, Mc Graw-Hill, 1993 Plant, Macolm. Basic Eletronics, London, SCDC Publications, 1990 Harowitz P.; Hill W.The Art of Eletronics, USA, Cambridge University Press, 1989.

Prof Franklin